# Neuromorphic Electronics for Energy Efficient Processing

Narayan Srinivasa

Center for Neural and Emergent Systems Information and Systems Sciences Lab HRL Laboratories LLC Malibu, CA

ITRS ERD Presentation, Stanford University 02/26/15

### Mammalian Brain vs. Computers: Architectural Aspects

#### Brain

- Operates at low speeds (< 10 Hz)

- Spike Encoding

- Power and energy efficient

- Asynchronous (no global clock) *clock free*

- Analog computing and communication

- Memory and computation are fully integrated

Small world network organization with *multi-scale interactions*

#### Computer

Operates at very high speeds (> GHz)

**Digital Encoding**

Power and energy hungry

Synchronous (global clock) – *clock* aligned

Digital computing and communication

Memory and computation are separated

Access to a single pre-determined scale with local interactions only

N. Srinivasa, Design considerations for a computational architecture of human cognition, *Emerging Nanoelectronic Devices*, First Edition, Ann Chen, James Hutchby, Victor Zhirnov and George Bourianoff, John Wiley and Sons, Ltd, January, 2015.

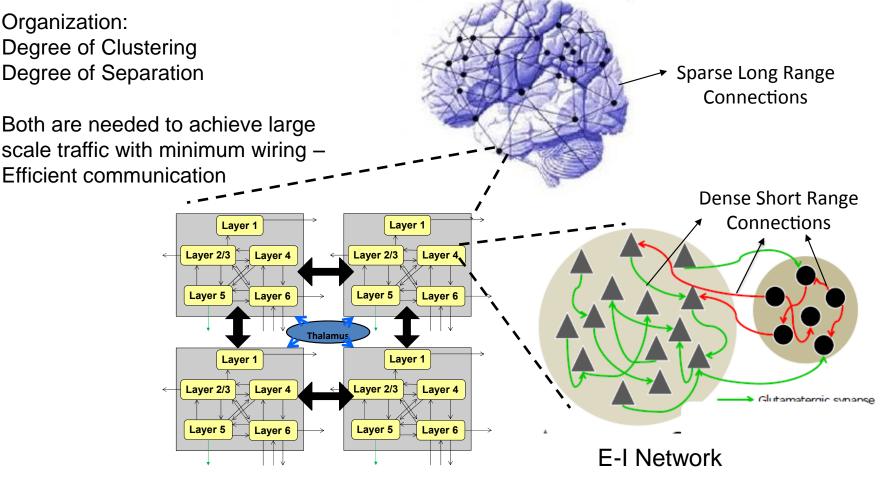

#### **Brain Architecture**

Evolutionary Objective: Keeping synaptic path length fairly constant with brain size

**Thalamocortical Circuits**

N. Srinivasa, Design considerations for a computational architecture of human cognition, *Emerging Nanoelectronic Devices*, First Edition, Ann Chen, James Hutchby, Victor Zhirnov and George Bourianoff, John Wiley and Sons, Ltd, January 2015.

#### Mammalian Brain vs. Computers: Other Features and Dynamics

#### Brain

Composed of faulty, noisy components that are short-lived but can regenerate – *fault tolerant*

Fully distributed processing that can integrate multiple sources of information and process multiple goals simultaneously - *grid-free*

Very limited encoding into symbols – *symbol-free*

Spontaneously active

Intelligence via Learning thru BBE interactions

#### Computer

Made of precise components which have longer lives but cannot regenerate – fault sensitive

Serial/Parallel processing that can integrate multiple sources of information towards a common goal

Encoding of concepts using symbols

No activity unless instructed

Intelligence via programmed algorithms

N. Srinivasa, Design considerations for a computational architecture of human cognition, *Emerging Nanoelectronic Devices*, First Edition, Ann Chen, James Hutchby, Victor Zhirnov and George Bourianoff, John Wiley and Sons, Ltd, January, 2015.

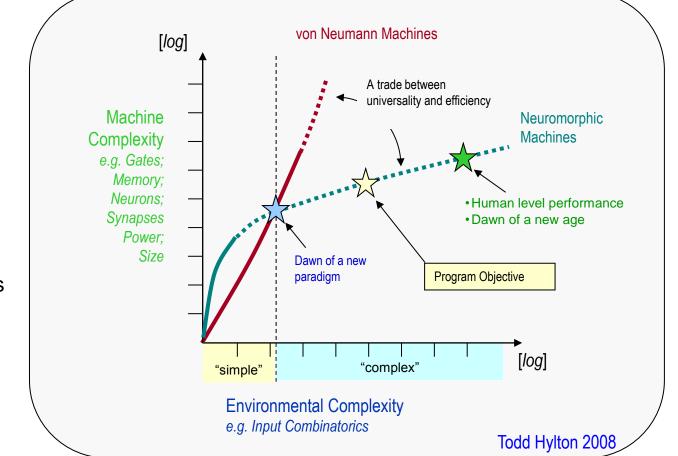

## DARPA SyNAPSE: Motivation and Objective

#### <u>Problem</u>

- As compared to biological systems, today's intelligent machines are less efficient by a factor of a <u>million</u> to a <u>billion</u> in complex environments.

- For intelligent machines to be useful, they must compete with biological systems.

The SyNAPSE program sought to break the programmable machine paradigm by developing neuromorphic machine technology that scales to biological levels

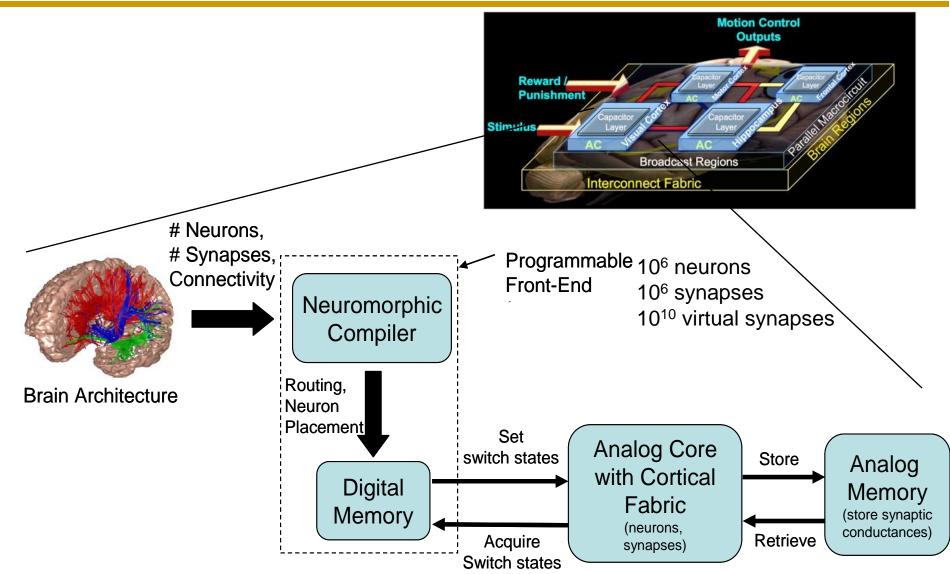

# Large Scale Neuromorphic System

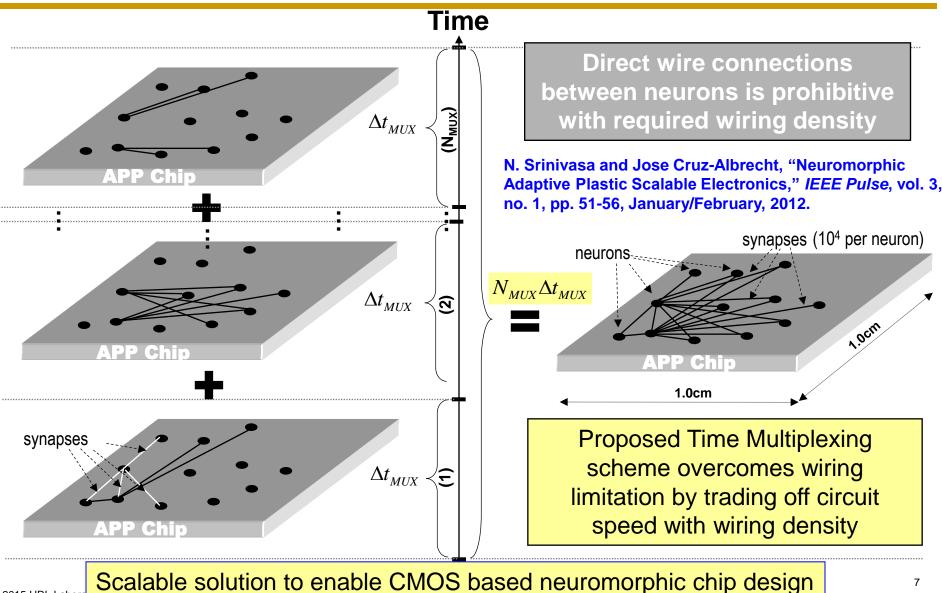

### Time Multiplexing Concept to **Address Connectivity Challenge**

Time-Multiplexed Fabric & Neuromorphic Compiler to address programmable connectivity challenge

K. Minkovich, N. Srinivasa, J. M. Cruz-Albrecht, Y. K. Cho and A. Nogin, "Programming Time-Multiplexed Reconfigurable Hardware Using a Scalable Neuromorphic Compiler," *IEEE Trans. on Neural Networks and Learning Systems*, vol. 23, no. 6, pp. 889-901, June 2012.

Time-multiplexing fabric with novel compiler ensures flexible connectivity in CMOS

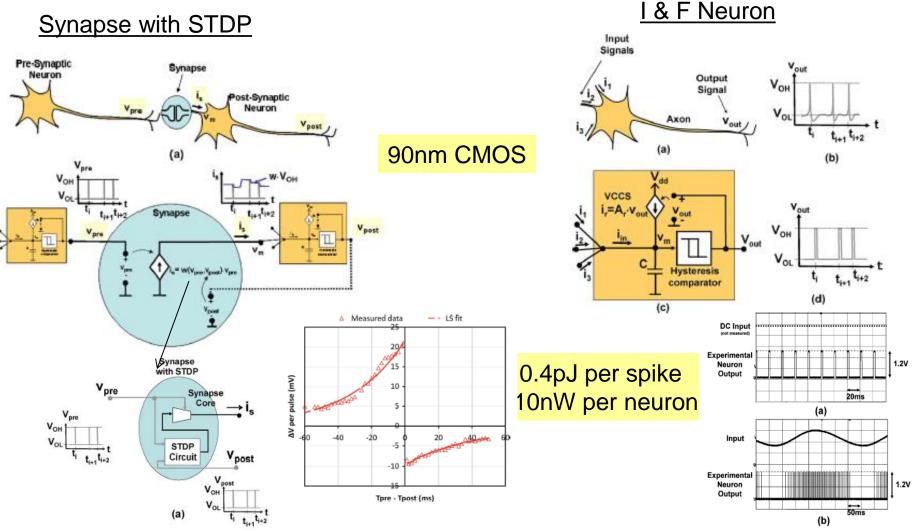

Mixed Signal CMOS neurons and synapses to address energy efficiency challenge

Jose Cruz-Albrecht, Michael Yung, Narayan Srinivasa, "Energy-Efficient, Neuron, Synapse and STDP Integrated Circuits," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 6. No. 3, pp. 246-256, June, 2012.

© 2015 HRL Laboratories, LLC. All Rights Reserved

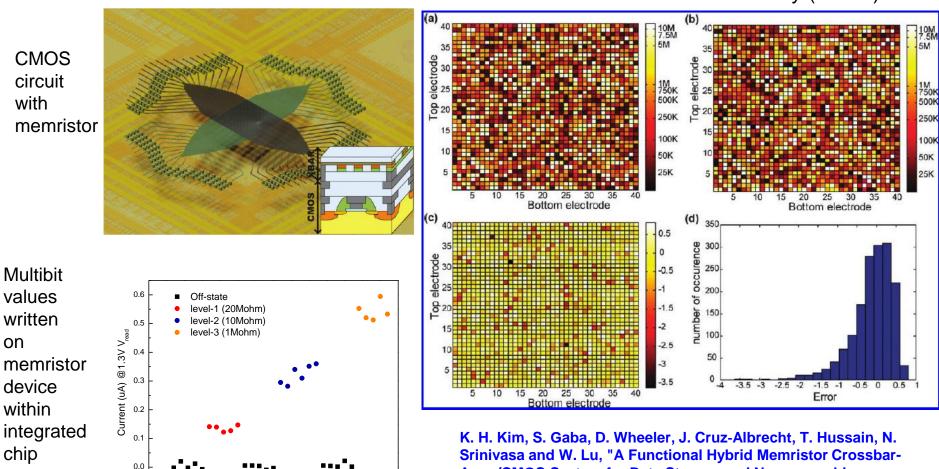

#### Analog memristor array with CMOS integration to address high density memory challenge (3\*10<sup>10</sup> bits/cm<sup>2</sup>)

Data written on memristor array (40x40)

K. H. Kim, S. Gaba, D. Wheeler, J. Cruz-Albrecht, T. Hussain, N. Srinivasa and W. Lu, "A Functional Hybrid Memristor Crossbar Array/CMOS System for Data Storage and Neuromorphic Applications" *Nano Letters*, vol.12, no. 1, pp. 389–395, February/March 2012.

#### HRL Proprietary

5

10

15

**Pulse Sequence**

20

25

30

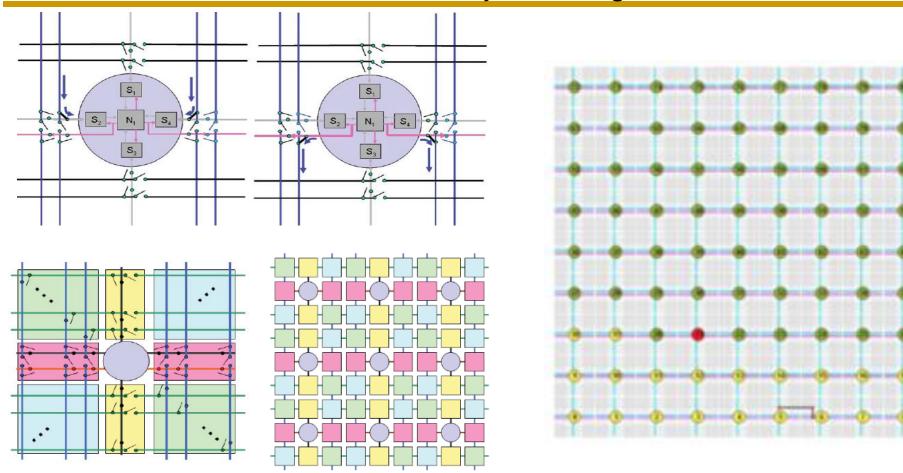

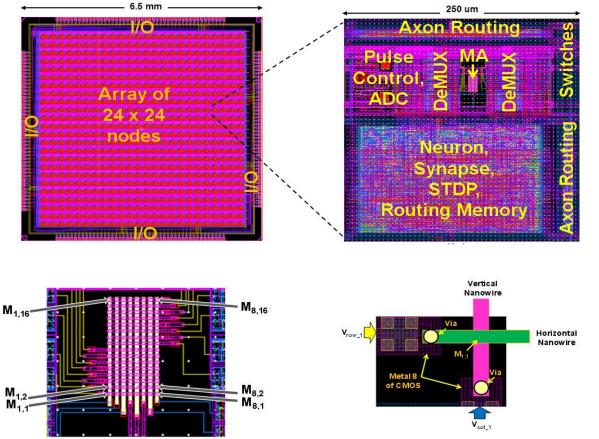

# HRL Neuromorphic Chip – Gen 1

- 576 point neurons with receptor kinetics

- > 9K synapses with STDP

- Synaptic time multiplexing

- Axonal delays

- Fully programmable

- 90 nm CMOS

- Integrated memristors

- SRAM

- ~ 36 mm<sup>2</sup>

- ~ 30 mW

J. Cruz-Albrecht, T. J. Derosier and N. Srinivasa, "Scalable neural chip with synaptic electronics using CMOS integrated memristors", *Nanotechnology*, Special Issue on synaptic electronics, September 2013. doi:10.1088/0957-4484/24/38/384011.

HRL neuromorphic chip provides a key starting point for the development of the real world applications with SWAP constraints

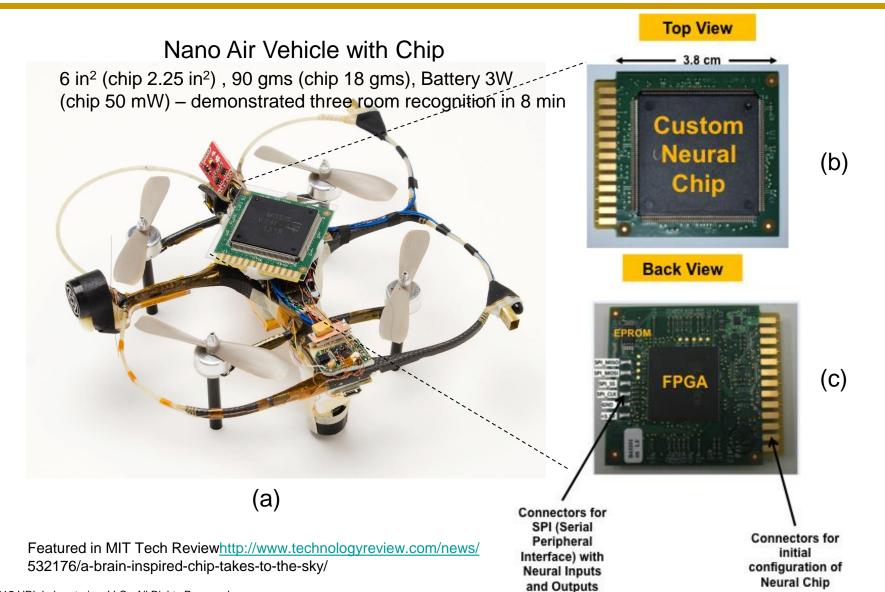

### NAV Experimental Integration for Room Recognition

12

- HRL neuromorphic technology enables

- spiking enables energy efficient processing

- can meet low SWAP requirements

- learning enables autonomous applications

- currently pursuing a variety of autonomous applications including some for our owners